Что такое тригеры —кратко

Термин триггер происходит от английского слова trigger — защёлка, спусковой крючок. Для обозначения этой схемы в английском языке чаще употребляется термин flip-flop, что в переводе означает “хлопанье”. Это звукоподражательное название электронной схемы указывает на её способность почти мгновенно переходить (“перебрасываться”) из одного электрического состояния в другое и наоборот.

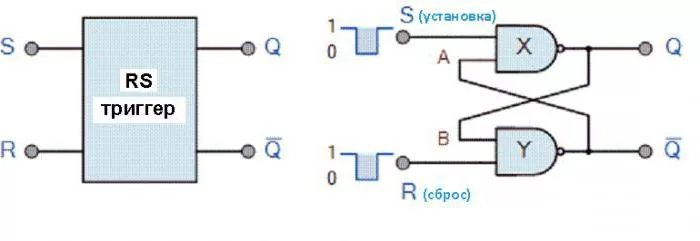

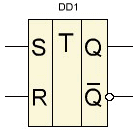

Самый распространённый тип триггера — так называемый RS-триггер (S и R, соответственно, от английских set — установка, и reset — сброс). Условное обозначение триггера — на рис. 5.6.

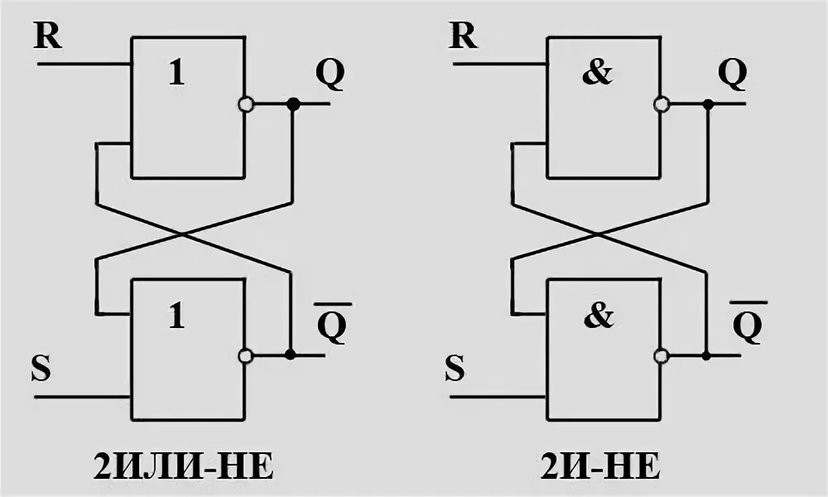

Он имеет два симметричных входа S и R и два симметричных выхода Q и , причем выходной сигнал Q является логическим отрицанием сигнала . На каждый из двух входов S и R могут подаваться входные сигналы в виде кратковременных импульсов ( ). Наличие импульса на входе будем считать единицей, а его отсутствие — нулем. На рис. 5.7 показана реализация триггера с помощью вентилей ИЛИ—НЕ и соответствующая таблица истинности.

| S | R | Q | |

| запрещено | |||

| 1 | 1 | ||

| 1 | 1 | ||

| 1 | 1 | хранение бита |

Проанализируем возможные комбинации значений входов R и S триггера, используя его схему и таблицу истинности схемы ИЛИ—НЕ (табл. 5.5).

- Если на входы триггера подать S=”1″, R=”0″, то (независимо от состояния) на выходе Q верхнего вентиля появится “0”. После этого на входах нижнего вентиля окажется R=”0″, Q=”0″ и выход станет равным “1”.

- Точно так же при подаче “0” на вход S и “1” на вход R на выходе появится “0”, а на Q — “1”.

- Если на входы R и S подана логическая “1”, то состояние Q и не меняется.

- Подача на оба входа R и S логического “0” может привести к неоднозначному результату, поэтому эта комбинация входных сигналов запрещена.

Поскольку один триггер может запомнить только один разряд двоичного кода, то для запоминания байта нужно 8 триггеров, для запоминания килобайта, соответственно, 8 х 210 = 8192 триггеров. Современные микросхемы памяти содержат миллионы триггеров.

Место триггеров в цифровой схемотехнике

В отличие от комбинационных логических схем, которые изменяют состояние в зависимости от фактических сигналов, поданных на их входы в определенное время, последовательностные логические имеют некоторую форму присущей им встроенной «памяти», так что они могут учитывать как предыдущее, так и фактическое состояние их входов и выходов. Общая структурная схема последовательностного устройства показана ниже.

RS-триггер как цифровой управляющий автомат включает собственно память и комбинационную схему управления на типовых лигических элементах, реализующую его входной логический алгоритм. Если рассматривать эту схему применительно к простейшим схемам триггеров, то они не имеют структурно выделенной памяти в виде какой-то специализированной микросхемы или схемного узла. Память триггера существует на уровне функции, она словно встроена в алгоритм работы его комбинационной схемы управления.

Проявлением этой «памяти» является так называемая бистабильность триггера, выходы которого могут находиться в одном из двух основных состояний: логической единицы (далее – 1) или логического нуля (далее – 0). Установившиеся значения своих выходов триггер запоминает («защелкивает» их) и сохраняет, пока не возникнет очередное изменение его входных сигналов.

Назначение

Основным назначением RS-триггеров является запись и хранение полученной информации. RS-триггер может легко оперировать данными и использовать их для периодического изменения общего состояния принципиальной схемы. Например, элемент может использоваться для включения определенных функций в электронной схеме.

Простой RS-триггер использует особый принцип работы, основанный на получении входных сигналов, которые в зависимости от поставленной задачи изменяют состояние выходов устройства. При входе сигнала на основной блок, на выходах происходит скачкообразное изменение напряжения, вследствие чего осуществляется управление поставленной задачей.

Логическое электронное устройство состоит из нескольких активных входных и выходных контактов. Рассмотрим эти контакты:

- Вход, использующийся для формирования выхода «Q». Его условное обозначение «R». На этом участке схемы происходит запись единицы.

- Вход, использующийся для сброса выхода «Q» обозначается буквой «S». На этом участке происходит запись нуля.

Далее рассмотрим, как работает простой RS-элемент.

Принцип работы простого RS-триггера невозможен без выходов. Они имеют такие обозначения:

- «Q» — является прямым выходом.

- «Q¯» — инверсный выход. В обозначение такого выхода добавлена черточка над буквой Q.

Самый первым был сделан триггер на транзисторах. Современные логические элементы сильно минимизированы, поэтому в основе всех таких устройств обязательно лежит микросхема. Такие устройства не подвержены воздействию помех, имеют низкий процент метастабильности, немного больше памяти и более широкие возможности для использования.

Транзисторные модели надежнее, но их основные недостатки: размер, наличие множества компонентов. Для увеличения памяти такие элементы подключаются параллельно в схему.

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

- асинхронные;

- синхронные (тактируемые).

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

- динамические;

- статические.

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Различие триггеров по функциональным возможностям

● с раздельной установкой состояния 0 и 1 (RS-триггеры);

● универсальные (JK-триггеры);

● с приемом информации по одному входу D (D-триггеры, или триггеры задержки);

● со счетным входом Т (Т-триггеры).

Входы триггеров обычно обозначают следующим образом:

S — вход для установки в состояние «1»;

R — вход для установки в состояние «0»;

J — вход для установки в состояние «1» в универсальном триггере;

К — вход для установки в состояние «0» в универсальном триггере;

Т — счетный (общий) вход;

D — вход для установки в состояние «1» или в состояние «0»;

V — дополнительный управляющий вход для разрешения приема информации (иногда используют букву Е вместо V).

Рассмотрим некоторые типы триггеров и их реализацию на логических элементах.

RS-триггер на логических элементах

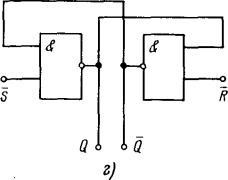

Простейший способ его сделать – соединить вместе пару двухвходовых логических элементов И-НЕ. При этом обратная связь с выхода одного элемента подается на вход другого (см. схему ниже).

Как правило, в данной схеме входные сигналы показывают инверсными (с верхним подчеркиванием), хотя в дальнейшем при анализе работы используют обозначения прямых (неинвертированных) входов. Это сильно затрудняет понимание логики работы триггера. Поэтому мы не будем вводить инвертирование входов на этапе рассмотрения работы схемы на элементах И-НЕ, а учтем это в дальнейшем при ее модификации.

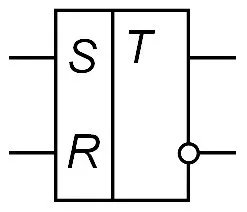

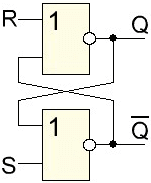

Сколько входов и выходов имеет RS-триггер? Из схемы выше видно, что он содержит S-вход и R-вход, которые служат, соответственно, для установки и сброса схемы, а также прямой Q и инверсный Q̃ выходы. Но данный простейший триггер относится к виду асинхронных, его условное обозначение показано ниже.

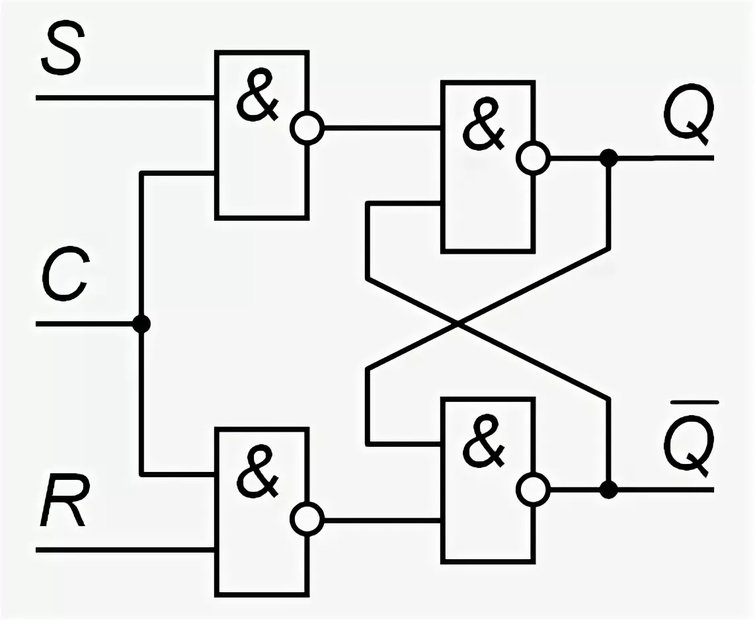

В синхронном устройстве имеется еще и вход C для тактовых импульсов.

Устройство и принцип работы RS-триггера

Одним из важнейших элементов цифровой техники является триггер (англ. Trigger – защёлка, спусковой крючок).

Сам триггер не является базовым элементом, так как он собирается из более простых логических схем. Семейство триггеров весьма обширно. Это триггеры: T, D, C, JK, но основой всех является самый простой RS-триггер.

Без RS триггеров невозможно было бы создание никаких вычислительных устройств от игровой приставки до суперкомпьютера. У триггера два входа S (set) – установка и R (reset) – сброс и два выхода Q-прямой и Q- инверсный. Инверсный выход имеет сверху чёрточку. Триггер бистабильная система, которая может находиться в одном из двух устойчивых состояний сколь угодно долго. На рисунке показан RS-триггер выполненный на элементах 2ИЛИ – НЕ.

Точно так же триггер может быть выполнен и на элементах 2И – НЕ.

Единственная разница это то, что триггер на элементах И – НЕ активируется, то есть переводится в другое состояние потенциалом логического нуля. Триггер, собранный на элементах ИЛИ – НЕ активируется логической единицей. Это определяется таблицей истинности логических элементов. При подаче положительного потенциала на вход S мы получим на выходе Q высокий потенциал, а на выходе Q низкий потенциал. Тем самым мы записали в триггер, как в ячейку памяти, единицу. Пока на вход R не будет подан высокий потенциал, состояние триггера не изменится.

На принципиальных схемах триггер изображается следующим образом.

Два входа R и S, два выхода прямой и инверсный и буква Т означающая триггер.

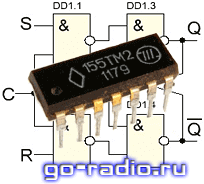

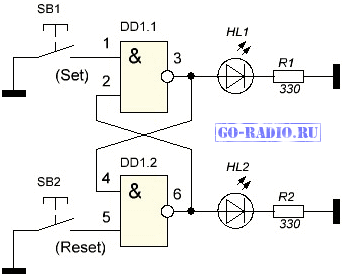

Хорошо отображает принцип работы RS-триггера несложная схема, собранная на двух элементах 2И – НЕ. Для этого используется микросхема 155ЛА3, которая содержит четыре таких элемента. Нумерация на схеме соответствует выводам микросхемы. Напряжение питания +5V подаётся на 14 вывод, а минус подаётся на 7 вывод микросхемы. После включения питания триггер установится в одно из двух устойчивых состояний.

Исходя из того, что сопротивление переходов транзисторов логических элементов не может быть абсолютно одинаковым, то триггер после включения питания, как правило, принимает одно и то же состояние.

Допустим, после подачи питания у нас горит верхний по схеме светодиод HL1. Можно сколько угодно нажимать кнопку SB1 ситуация не изменится, но достаточно на долю секунды замкнуть контакты кнопки SB2 как триггер поменяет своё состояние на противоположное. Горевший светодиод HL1 погаснет и загорится другой – HL2. Тем самым мы перевели триггер в другое устойчивое состояние.

На данной схеме всё достаточно условно, а на реальном триггере принято считать, что если на прямом выходе “Q” высокий уровень то триггер установлен, если уровень низкий то триггер сброшен.

Основной недостаток рассматриваемого триггера это, то, что он асинхронный. Другие более сложные схемы триггеров синхронизируются тактовыми импульсами общими для всей схемы и вырабатываемые тактовым генератором. Кроме того сложная входная логика позволяет держать триггер в установленном состоянии до тех пор пока не будет сформирован сигнал разрешения смены состояния триггера.

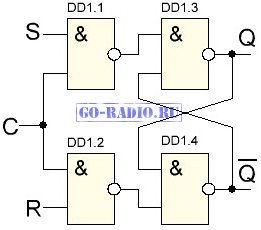

RS-триггер может быть и синхронным, но двух логических элементов для этого мало.

На рисунке изображена схема синхронного RS-триггера. Такой триггер может быть собран на микросхеме К155ЛА3, которая содержит как раз четыре элемента 2И – НЕ. В данной схеме переключение триггера из одного состояния в другое может быть осуществлено только в момент прихода синхроимпульса на вход “C”.

На рассмотренной выше схеме переключение триггера осуществляется с помощью кнопок. Такой вариант используется достаточно часто и именно для кнопочного управления какой-либо аппаратурой. В электронике существует понятие «дребезг контактов» то есть, когда мы нажимаем кнопку, на вход устройства проникает целый пакет импульсов, который может привести к серьёзным нарушениям в работе. Использование RS-триггера позволяет избежать этого.

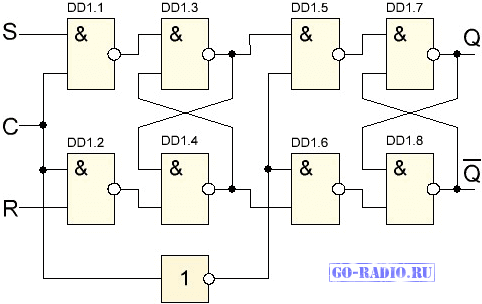

Благодаря своей простоте и недорогой стоимости RS-триггеры широко применяются в схемах индикации. Часто для повышения надёжности и устранения возможности случайного срабатывания RS-триггер собирается по так называемой двухступенчатой схеме. Вот схема.

Здесь можно видеть два совершенно одинаковых синхронных RS-триггера, только для второго триггера синхроимпульсы инвертируются. Первый триггер в связке называют M (master) – хозяин, а второй триггер называется S (slave) – раб.

Допустим на входе “С” высокий потенциал. М-триггер принимает информацию, но низкий потенциал на входе синхронизации S-триггера блокирует приём информации. После того как потенциал поменялся на противоположный информация из M-триггера записывается в S-триггер, но приём информации в M-триггер блокируется.

Такая двухступенчатая система намного надёжнее обычного RS-триггера. Она свободна от случайных срабатываний.

Для более наглядного изучения работы RS-триггера рекомендую провести эксперименты с RS-триггером.

Синхронный RS-триггер

Основное назначение триггера в цифровых схемах – хранить выработанные логическими схемами результаты. Для отсечения еще не установившихся, искаженных переходными процессами результатов между выходом какой-либо логической схемы и входами триггера ставят ключи в виде элементов И-НЕ. Действие этого сигнала аналогично разрешающему сигналу

в схеме дешифратора (рис. 4.2 в “Функциональные узлы комбинаторной логики. Дешифраторы” ). На первый и второй логические элементы И-НЕ одновременно поступает синхросигнал

При неактивном уровне

на выходах первого и второго логических элементов И-НЕ будет логическая

. Она не является решающей для функции И-НЕ, поэтому триггер на третьем и четвертом элементах будет хранить записанную ранее информацию. Таким образом, триггер не реагирует на изменения входных сигналов при

. Если же синхросигнал становится активным (

), то схема пропускает все переключения входных сигналов

и

Поскольку входные ключи производят инверсию входных сигналов

и

, активным их уровнем будет логическая

Синхронный RS-триггер: а – функциональная схема; б – УГО

Таблица 7.3. Таблица истинности синхронного RS-триггераУправляющие сигналыСостояние выходовРежим работы

|  | Хранение ранее записанной информации | |||

| 1 | |||||

| 1 | |||||

| 1 | 1 | ||||

| 1 |  |  | Хранение ранее записанной информации | ||

| 1 | 1 | 1 | Сброс триггера | ||

| 1 | 1 | 1 | Установка триггера | ||

| 1 | 1 | 1 | Неустойчивое состояние |

Недостатком схемы остается наличие недопустимой комбинации на входе, при которой получается неустойчивое состояние схемы.

Состояние «Установлен»

Рассмотрим, как происходит работа RS-триггера в этом состоянии, задаваемом значениями R = 0 и S = 1. Поскольку на вход R элемента И-НЕ Y подан уровень 0, то Q̃ =1 (логика И-НЕ). С выхода Y сигнал Q̃ также подан обратно на элемент X (вход “A”). Поскольку S = A = 1, то Q = 0.

Если устанавливается R = 1, а вход S по-прежнему равен 1, то на входах Y имеем B = 0 и R = 1, а его выход Q̃ =1, т. е. он не изменился. Итак, если S = 1, то RS-схема триггера «защелкивается» в состоянии «Установлен» Q = 0 и Q̃ = 1, а смена сигнала R его не изменяет.

Состояние «Сброшен»

В этом втором устойчивом состоянии Q̃ = 0, а Q = 1, и задается оно входами R = 1 и S = 0. Поскольку у элемента Х вход S = 0, то его выход Q =1 (логика И-НЕ). Сигнал Q подается обратно на элемент Y (вход “В”), и так как R = B = 1, то Q̃ = 0.

Если S становится равен 1 при R = 1, то Q̃ остается равен лог 0, т. е. он не изменяется. Итак, при R =1 схема триггера снова «защелкивается» в состоянии «Сброшен» Q̃ = 0 и Q = 1, сохраняемом при любом сигнале S.

Сводим результаты в таблицу

Мы можем определить состояние сигналов Q и Q̃ по следующей таблице истинности:

| Состояние | S | R | Q | Q̃ | Описание |

| Установка | 1 | 1 | Выход Q̃ =1 | ||

| 1 | 1 | 1 | без изменений | ||

| Сброс | 1 | 1 | Выход Q̃ =0 | ||

| 1 | 1 | 1 | 1 | без изменений | |

| Недопустимое | 1 | 1 | состояние ошибки |

Видно, что когда S = R = 1, то Q и Q̃ могут быть равны как 1, так и 0 (но не одновременно!) в зависимости от уровней входов S или R перед возникновением данного состояния выходов. Таким образом, при условии S = R = 1 нельзя изменить состояние выходов Q и Q̃. Оно может измениться только при смене уровня с 1 на 0 на одном из входов.

Значение S = R = 0 является нежелательным или недопустимым состоянием, и его следует избегать. Состояние S = R = 0 вызывает установку обоих выходов Q и Q̃ на уровне 1, в то время как состояние Q̃ всегда должно быть обратно Q. Результатом является то, что триггер теряет контроль над Q и Q̃, и если два входа теперь перейдут к состоянию 1, то схема становится неустойчивой и переключается в неопределенное состояние.

RS-триггер. функциональные схемы, таблица переходов

Триггер – простейшее устройство, представляющее собой цифровой автомат. Он имеет два состояния устойчивости. Одному из этих состояний присваивается значение «1», а другому – «0». Состояние триггера, а также значение двоичной информации, которая в нем хранится, определяется выходными сигналами: прямым и инверсным. В том случае, когда на прямом выходе установится потенциал, который соответствует логической единице, состояние триггера называется единичным (при этом потенциал на инверсном выходе равен нулю). Если же на прямом выходе нет потенциала, то состояние триггера называется нулевым.

Классифицируют триггеры по следующим признакам:

1. По способу записываемой информации (асинхронные и синхронные).

2. По способу управлением информацией (статистические, динамические, одноступенчатые, многоступенчатые).

3. По способу реализации логических связей (JK-триггер, RS-триггеры, T-тригер, D-триггер и других типов).

Основными параметрами всех типов триггеров являются наибольшее значение длительности входного сигнала, время задержки необходимого для переключения триггера, а также разрешающее время срабатывания.

В этой статье поговорим о таком типе устройств, как RS-триггер. Они бывают двух типов: синхронные и асинхронные.

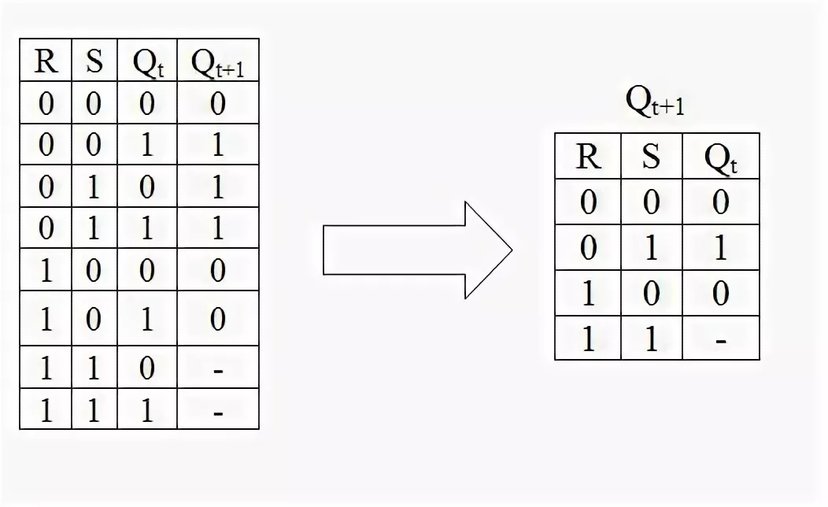

Асинхронный RS-триггер конструктивно имеет два прямых (R и S) входа. Это устройство функционирует согласно таблице переходов.

Запрещенной для такого триггера является комбинация сигналов на входах устройства, вызывающая состояние неопределенности. Эта комбинация может быть выражена требованием RtSt=0. При минимизации карты Карно выводится закон функционирования триггера, который называют характеристическим уравнением: Q(t+1)=St V R’tQt. При этом RtSt будет равно нулю.

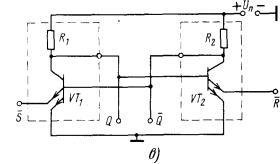

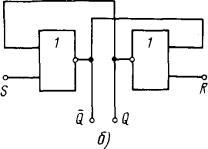

На функциональной схеме изображен RS-триггер асинхронного типа на элементах И-НЕ и во втором исполнении на элементах ИЛИ-НЕ.

Второй тип – синхронный RS-триггер. Такое устройство конструктивно имеет три прямых входа S, R, и C. Отличие триггера синхронного типа от асинхронного заключается в наличии входа синхронизации (С). Он необходим по следующим причинам: ведь на входы устройства (логического элемента) сигналы поступают не всегда одновременно. Это связано с тем, что они проходят через различные типы и количество узлов, которые обладают разной задержкой. Это явление называют «состязанием». В результате таких «состязаний» полученные значения сигналов будут накладываться на предыдущие значения других сигналов. Все это приводит к ложному срабатыванию устройства.

Это явление можно устранить подачей на вход устройства сигналов временного стробирования. А именно: на вход логического элемента, кроме непосредственно информационных сигналов, подаются ключевые синхронизирующие импульсы, к этому моменту информационные входные сигналы успеют зафиксироваться на входах.

Главное условие правильности работы срабатывания логических каскадов в RS-триггере и управляемых ими логических схем – недопустимость одновременного действия сигнала Rt или St, переключающего устройство, и съема информации с выхода Q(t+1) триггера. В связи с этим в потенциальных сериях элементов содержатся только синхронные.

RS-триггер синхронного типа представлен характеристическим уравнением: Q(t+1)=StCt V R’tQt V QtC’t.

На фото изображен RS-триггер синхронного типа на элементах И-НЕ.

Входные логические элементы И-НЕ передают переключающую логическую единицу с информационного входа S или R на необходимые входы асинхронного триггера типа RS с инверсными входами только при условии наличия на синхронном входе (С) сигнала с уровнем логической единицы.

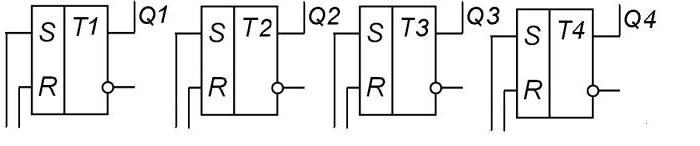

Регистры на триггерах

RS-триггер способен сохранять 1 бит цифровой информации. Если необходимо хранить несколько бит, например, цифровое двоичное слово из нескольких двоичных разрядов (в микроконтроллерах обычно 8 или 16), то триггеры могут соединяться параллельно, образуя регистры. Это простейшие устройства для временного хранения набора двоичных цифровых разрядов, в которых каждый триггер сохраняет значение одного разряда (0 или 1. т. е. один бит). Так, показанный ниже 4-разрядный регистр на RS-триггерах содержит четыре отдельных триггера.

Любое двоичное число от (0000)2 до (1111)2 может быть сохранено в этом регистре просто путем установки или сброса соответствующего триггера. Давайте предположим, что первый триггер установлен (Q1 = 1), второй сброшен (Q2 = 0), третий также сброшен (Q3 = 0), а четвертый установлен (Q4 = 1). Тогда двоичное число, записанное в регистр, будет (1001)2.

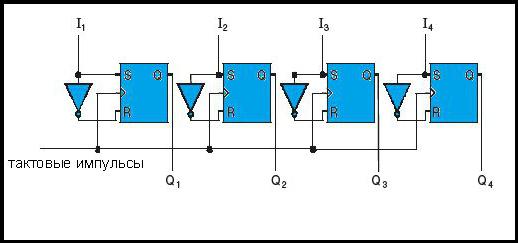

Кроме параллельных регистров, предназначенных для хранения цифровых слов, на RS-триггерах делаются и так называемые регистры сдвига, в которых разряды цифрового слова последовательно с приходом каждого тактового импульса сдвигаются влево или вправо на один разряд. Схема такого устройства на синхронных триггерах показана ниже.

Подобные регистры находят применение в схемах последовательных интерфейсов, когда поступающие из управляющего контроллера цифровые слова побитно передаются в линию связи.

Таблица истинности

D триггер — устройство и элементы с управлением по фронту

Таблица переходов состояний (таблица истинности) поясняет работу RS-триггера на элементах «И-НЕ». На ней Q 0 – текущий статус ячейки до попадания активного сигнала на порт. Когда логическая единица отсутствует на входах R и S, «защёлка» сохраняет положение Q 0. Активный импульс R = 1 перекидывает защёлку в положение 0, импульс S = 1 – в положение 1. Звездочка в таблице указывает на положение при запрещенном сочетании приходящих сигналов.

Таблица истинности RS-триггера

Такой тип имеет раздельное назначение логических состояний нуля и единицы по информационным портам.

Временные диаграммы

Импульсный стабилизатор напряжения

Кроме таблиц истинности, помогает разобраться в работе ячейки битовой памяти временная диаграмма. При этом на графике при изучении импульсов рассматривают следующие параметры:

- длительность импульса – временной интервал от фронта до спада;

- период – интервал от фронта предыдущего импульса до фронта последующего;

- скважность – отношение периода импульса к его длительности.

Диаграмма графически отображает сигнальные импульсы на входах и выходах в одних и тех же временных точках.

Временная диаграмма RS-триггера

Диаграмма переключения RS-триггера

Состояния переключения, установки и сброса можно просмотреть на временной диаграмме. На ней отмечено, что переключатель переходит в положение установки при появлении нуля на его S-входе и единице на входе R, фиксированный сброс при подаче нуля на порт R и единицы на S.

Диаграмма переключения защёлки

Внимание! Если ноль подать на два входа (R и S) синхронно, то переключатель из-за неопределённого состояния на вводах может перевернуться в любое непредсказуемое положение, при этом произойдёт повреждение данных.

Еще несколько полезных моментов

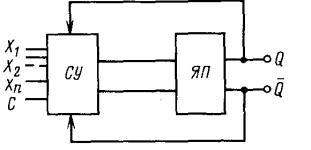

Общие сведения. Помимо логических элементов, реализующих основные логические операции, в цифровой технике широко используются в качестве базовых элементов ячейки памяти на основе разнообразных триггеров. Обобщенная модель триггера показана на рис. 3.6. Очевидно, любой триггер состоит из схемы управления (СУ) и бистабильной ячейки памяти (ЯП). Триггеры имеют входы управляющих сигналов Х1, Х2,…Хn два взаимоинверсных выхода Q и , а также могут иметь вход синхронизации С.

В общем случае к триггерам относят устройства, имеющие два устойчивых состояния, которые устанавливаются при подаче соответствующей комбинации сигналов на управляющие входы и сохраняются в течение заданного времени после окончания действия этих сигналов. Триггеры способны хранить двоичную информацию (состояния «О» и «1») после окончания действия входных импульсов. Это свойство обусловлено тем, что устройством управляют не только внешние сигналы, но и сигналы обратной связи самого триггера.

По функциональному признаку, определяющему поведение триггера при воздействии сигнала управления и способа управления, триггеры подразделяют на следующие типы:

- RS-триггеры, имеющие два управляющих входа: S (set— установка) и R (reset—сброс); D-триггеры (D—delay—задержка), имеющие один информационный вход;

- Т—триггеры (T—time—время, характеризующее внутреннюю задержку), переключающиеся в противоположное состояние с приходом каждого очередного входного импульса.

- Часто Т-триггеры называют триггерами со счетным запуском. Иногда Т-триггеры обозначают MS. Это отражает то, что каждый из них состоит из двух RS-триггеров, один из которых является основным (М—master—хозяин), а другой—вспомогательный (S—slave—раб);

- JK—универсальные триггеры, имеющие управляющие входы J (J—-jump—прыжок, переброс) и К (keep—держать, сохранять) и допускающие установку выходных уровней при наличии сигнала на входе синхронизации С.

По способу управления триггеры подразделяют на асинхронные и тактируемые. В асинхронных триггерах переключение из одного состояния в другое осуществляется непосредственно с поступлением сигнала на информационный вход. В тактируемых триггерах переключение производится только при наличии разрешающего, тактирующего импульса на входе синхронизации.

В зависимости от типа используемых ячеек памяти триггеры подразделяются на статические, статико-динамические и динамические. Первые два типа реализуются на основе логических элементов НЕ, ИЛИ-

НЕ, И-НЕ, а последний на основе МДП транзисторов.

В зависимости от типа базовых логических элементов реализуются триггеры с различными параметрами: быстродействием, потребляемой мощностью, нагрузочной способностью и др.

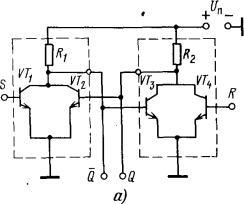

Как видно из рассмотрения принципиальных схем, основу триггеров составляют два инвертора, связанные между собой взаимными перекрестными связями. Эти связи обусловливают в процессе переключения возникновение положительной обратной связи, способствующей повышению быстродействия и надежности работы схемы.

При наличии логической 1 на выходе одного инвертора на выходе другого поддерживается логический 0. Необходимые уровни напряжения на выходе издаются схемой управления, которая при использовании логических элементов семейства ТЛНС (см. рис. 3.7, а) образована транзисторами VT1 и VT2, а при использовании элементов семейства ТТЛ (см. рис. 3.7, в) образована эмиттерными переходами транзисторов VT1 и VT2. Триггеры, реализованные на основе логических элементов ИЛИ-НЕ, работают в положительной логике, а реализованные на основе логических элементов И-НЕ работают в отрицательной логике. Для работы в положительной логике схема управления последних усложняется добавлением двух инверторов.

Уровни напряжений на обоих выходах триггера различны и одновременно изменяются на противоположные при работе устройства управления. Поэтому на условном обозначении триггера (см. рис. 3.7, б, г) один из выходов обозначен Q, а второй—через (факт инверсии отражается кружком на стороне прямоугольника). Выход Q считается главным: значениями Q характеризуют состояние триггера в целом.

Уравнение состояний RS-триггера имеет вид Здесь индексами n и n+1 обозначены значения величины Q до и после поступления управляющих сигналов. Используя это уравнение, можно определить возможные состояния триггера при разных наборах управляющих сигналов:

- если S = 0, R = 0, то , т.е. триггер сохраняет прежнее состояние;

- если S = 0, R = 1, то , т.е триггер по основному выходу находится в состоянии логического ;

- если S = 1, R = 0, то , т.е. триггер по основному выходу находится в состоянии логической 1;

если S = 1 и R = 1, то триггер находится в неопределенном состоянии Х, (т.е. с равной вероятностью может находиться в любом из устойчивых состояний Q = 1 или Q = 0), поэтому такой набор является запрещенным: нельзя одновременно подавать на триггер противоположные команды S (установить 1) и R (установить 0).

Наибольшей универсальностью среди триггеров обладает JK-триггер Он работает как RS-триггер, причем в отличие от RS-триггеров здесь допустимо, чтобы оба управляющих сигнала были равны 1.

Если управляющие сигналы J и К равны 1, то JK-триггер работает как T-триггер. При подаче на вход С синхронизирующего импульса триггер будет работать в режиме делителя на 2. Этот режим используется при построении последовательных счетчиков и делителей частоты любой сложности.

Если на информационные входы J и К подавать противофазные логические сигналы, то триггер будет работать в режиме синхронной записи информации. При подаче тактового импульса на вход С эта информация появляется на выходе, т. е. сдвигается в следующую ячейку Такой режим используется при построении сдвигающих регистров, распределителей импульсов, синхронных.

Интегральные JK-триггеры часто имеют несколько управляющих J, К входов, что расширяет его функциональные возможности и позволяет экономить внешние логические элементы. С помощью указанных входов триггер можно установить в определенное состояние независимо от тактового импульса. Поэтому эти входы получили названия предустановки и стирания.

Квазистатические триггеры в отличие от динамических не требуют так называемого «тактового питания» в период хранения информации. При записи информации тактовое питание необходимо, оно осуществляется тактовыми импульсами, имеющими длительность, меньшую, чем постоянная времени заряда и разряда паразитных емкостей затворов МДП транзисторов схемы. По сравнению со схемами статического типа квазистатические и динамические схемы триггеров позволяют в 2—3 раза уменьшить число используемых МДП транзисторов.

В динамических триггерах по истечении времени хранения информация теряется. Для сохранения информации необходимо ее периодическое восстановление путем подачи последовательности внешних импульсов, период которых Т меньше времени хранения информации t. Эти импульсы одновременно выполняют функции синхронизации. В зависимости от числа последовательностей синхроимпульсов различают двух- и четырехфазные динамические элементы.

Характерной особенностью цифровых устройств на основе динамических триггеров является то, что синхронизация в них осуществляется путем подключения и отключения соответствующих элементов к цепи питания. При этом элементы потребляют мощность от источника питания не постоянно, а периодически в течение относительно коротких промежутков времени, когда производится переключение элементов или восстановление информации. В результате устройства на динамических элементах при низких частотах переключения потребляют существенно меньшую мощность, чем на основе статических триггеров. Поэтому динамические триггеры являются весьма перспективными элементами для БИС памяти. Рассмотрим принцип действия динамического триггера, пригодного для использования в качестве ячейки памяти БИС.

На рис. 3.8 изображена схема динамического триггера на основе двух инверторов VT1, VT3 и VT2, VТ4, с взаимными перекрестными связями. В триггере используются МДП транзисторы с каналом р-типа. Питание и синхронизация работы триггера производятся импульсными последовательностями, подаваемыми в разрядные шины РШ и РШ1 (в них потенциалы могут принимать значения –Un, 0 B). Хранение информации обеспечивается паразитными емкостями МДП транзисторов, для удобства обозначенными С1 и С2.

Для записи на адресную шину подают напряжение –Un, а на разрядные шины РШ1 и РШ подают уровни –Un и 0. Уровень –Un через ключ VT4 поступает на вход транзистора VT1 и открывает его. На затвор транзистора VT2 поступает уровень 0, и, следовательно, он закрывается. Напряжение на емкости С1 принимает значение uC1 = –Un, а на емкости С2 равно нулю (иC1=0). После записи отключают напряжение на адресной шине.

ПредыдущаяТак как остаточный ток закрытого транзистора VT1 мал, то емкость С1 будет сохраняться на выходах ячейки (на стоках VT1 и VT2) длительное время За это время можно несколько раз считывать информацию ячейки (следует учитывать что при считывании приходится открывать транзистор VT4 и разряд С1 ускоряется). Для того чтобы поддерживать напряжение на емкости С1, несмотря на неизбежный ее разряд, осуществляют регенерацию: периодическую запись того же кода.