Триггер — что это за устройство

Он представляет собой электронное устройство, способное на протяжении длительного времени сохранять одно из двух или нескольких состояний. Это происходит до тех пор, пока на него подаётся электропитание. Существует несколько типов триггеров, каждый из которых имеет свою сферу применения. Фактически они являются базовыми элементами. На их основе создаются различные цифровые электронные устройства.

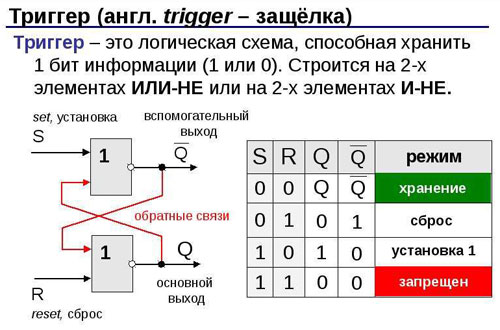

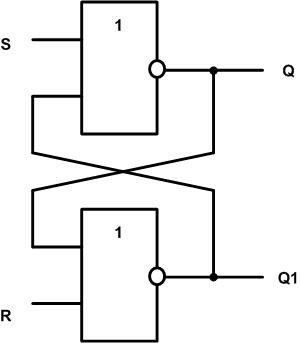

Триггер способен на протяжении довольно длительного промежутка времени пребывать в одном устойчивом режиме из нескольких возможных, а затем под действием входных сигналов переходить из одного режима в другой. Состоит он из элементарных логических элементов, функционирующих по правилам математической логики. Это могут быть ИЛИ-НЕ и И-НЕ. Первые из них функционируют в одноединичном прямом коде, то есть, на выходе одного из элементов будет 1, а на выходах других — 0. Устройство с элементами второго вида работает в однонулевом инверсном коде: на выходе одного из них 0, а на выходах других — 1.

Триггер – элемент цифровой техники, бистабильное устройство, которое переключается в одно из состояний и может находиться в нем бесконечно долго даже при снятии внешних сигналов. Он строится из логических элементов первого уровня (И-НЕ, ИЛИ-НЕ и т.д.) и относится к логическим устройствам второго уровня.

На практике триггеры выпускаются в виде микросхем в отдельном корпусе или входят в качестве элементов в состав больших интегральных схем (БИС) или программируемых логических матриц (ПЛМ).

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

- асинхронные;

- синхронные (тактируемые).

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

- динамические;

- статические.

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

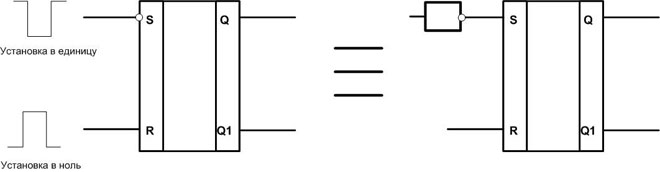

RS-триггер

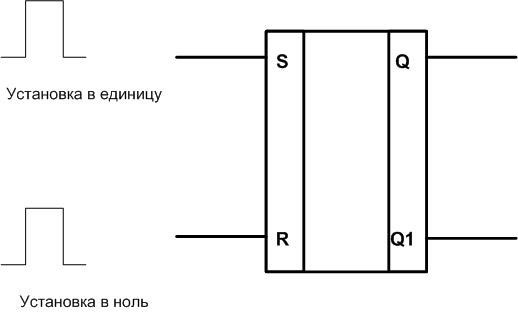

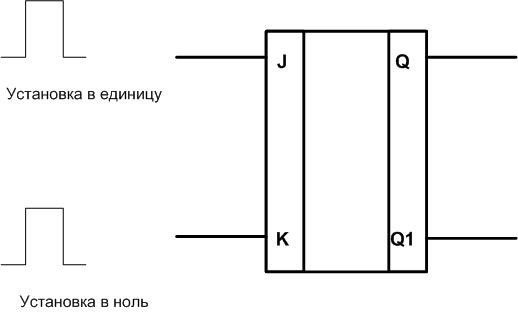

Самый распространенный тип асинхронного бистабильного устройства – RS-триггер. Он относится к триггерам с раздельной установкой состояния 0 и 1. Для этого имеется два входа:

- S — set (установка);

- R — reset (сброс).

Имеется прямой выход Q, также может быть инверсный выход Q1. Логический уровень на нём всегда противоположен уровню на Q – это бывает удобно при разработке схем.

При подаче положительного уровня на вход S на выходе Q установится логическая единица (если есть инверсный выход, он перейдет на уровень 0). После этого на входе установки сигнал может меняться как угодно – на выходной уровень это не повлияет. До тех пор, пока единица не появится на входе R. Это установит триггер в состояние 0 (1 на инверсном выводе). Теперь изменение сигнала на входе сброса никак не повлияет на дальнейшее состояние элемента.

Важно! Вариант, когда на обоих входах присутствует логическая единица, является запретным. Триггер установится в произвольное состояние. При разработке схем такой ситуации надо избегать.

RS-триггер можно построить на основе широко распространенных двухвходовых элементов И-НЕ. Такой способ реализуем как на обычных микросхемах, так и внутри программируемых матриц.

Один или оба входа могут быть инверсными. Это означает, что по этим выводам триггер управляется появлением не высокого, а низкого уровня.

Если построить RS-триггер на двухвходовых элементах И-НЕ, то оба входа будут инверсными – управляться подачей логического нуля.

Существует стробируемый вариант RS-триггера. У него имеется дополнительный вход С. Переключение происходит при выполнении двух условий:

- присутствие высокого уровня на входе Set или Reset;

- наличие тактового сигнала.

Такой элемент применяют в случаях, когда переключение надо задержать, например, на время окончания переходных процессов.

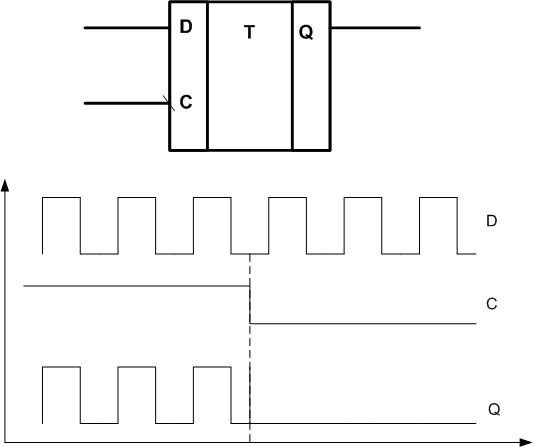

D-триггер («прозрачный триггер», «защелка», latch) относится к категории синхронных устройств, тактируемых по входу С. Также имеется вход для данных D (Data). По функциональным возможностям устройство относится к триггерам с приёмом информации по одному входу.

Пока на входе для синхронизации присутствует логическая единица, сигнал на выходе Q повторяет сигнал на входе данных (режим прозрачности). Как только уровень строба перейдет в состояние 0, на выходе Q уровень останется тем же, что был в момент перепада (защелкнется). Так можно зафиксировать входной уровень на входе в любой момент времени. Также существуют D-триггеры с тактированием по фронту. Они защёлкивают сигнал по положительному перепаду строба.

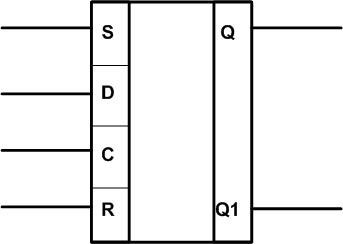

На практике в одной микросхеме могут объединять два типа бистабильных устройств. Например, D и RS-триггер. В этом случае входы Set/Reset являются приоритетными. Если на них присутствует логический ноль, то элемент ведёт себя как обычный D-триггер. При появлении хотя бы на одном входе высокого уровня, выход устанавливается в 0 или 1 независимо от сигналов на входах С и D.

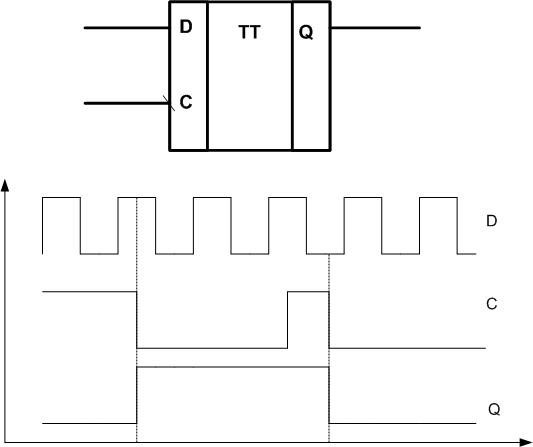

Прозрачность D-триггера не всегда является полезным свойством. Чтобы её избежать, применяются двойные элементы (flip-flop, «хлопающий» триггер), они обозначаются литерами TT. Первым триггером служит обычная защёлка, пропускающая входной сигнал на выход. Второй триггер служит элементом памяти. Тактируются оба устройства одним стробом.

JK-триггеры

Этот бистабильный элемент относится к категории универсальных. Он может управляться раздельно по входам. Логика работы JK-триггера похожа на работу RS-элемента. Для установки выхода в единицу используется вход J (Job). Появление высокого уровня на выводе K (Keep) сбрасывает выход в ноль. Принципиальным отличием от RS-триггера является то, что одновременное появление единиц на двух управляющих входах не является запретным. В этом случае выход элемента меняет свое состояние на противоположное.

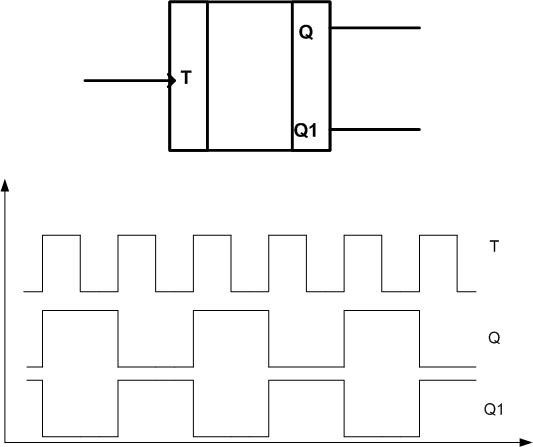

Если выходы Job и Keep соединить, то JK-триггер превращается в асинхронный счётный Т-триггер. Когда на объединённый вход подаётся меандр, на выходе будет в два раза меньшая частота. Как и у RS-элемента, существует тактируемый вариант JK-триггера. На практике применяются, в основном, именно стробируемые элементы такого типа.

T-триггеры

T-триггер относится к классу счётных бистабильных элементов. Логика его работы проста – он изменяет своё состояние каждый раз, когда на его вход приходит очередная логическая единица. Если на вход подать импульсный сигнал, выходная частота будет в два раза выше входной. На инверсном выходе сигнал будет противофазен прямому.

Так работает асинхронный Т-триггер. Также существует синхронный вариант. При подаче импульсного сигнала на тактирующий вход и при наличии логической единицы на выводе T, элемент ведёт себя так же, как и асинхронный – делит входную частоту пополам. Если на выводе Т логический ноль, то выход Q устанавливается в низкий уровень независимо от наличия стробов.

Универсальный триггер

JK-триггер

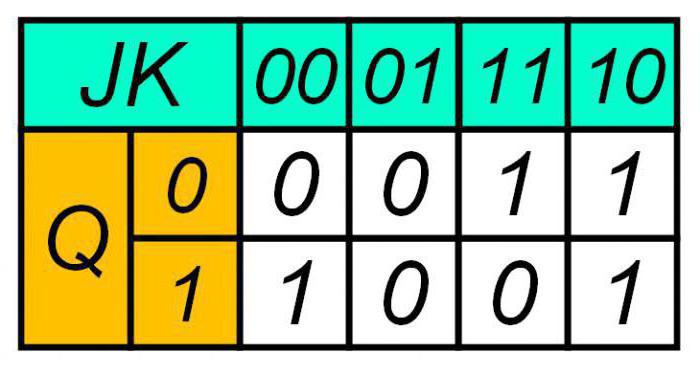

JK-триггером называют автомат Мура с двумя устойчивыми состояниями и двумя входами J и K, который при условии J * K = 1 осуществляет инверсию предыдущего состояния (т.е. при J*K=1, Q(t+1) = Q(t)), а в остальных случаях функционируют в соответствии с таблицей истинности RS триггера, при этом вход J эквивалентен входу S, а вход K — входу R. Этот триггер уже не имеет запрещенной комбинации входных сигналов и его таблица истинности, то есть зависимость Q(t+1) = f[J, K, Q(t)] имеет вид:

Таблица истинности JK-триггера:

| J | K | Q(t) | Q(t+1) |

По этой таблице можно построить диаграмму Вейча для Q(t+1), которую можно использовать для минимизации, и матрицу переходов:

| KQ(t) |

| J |

Матрица переходов JK-триггера:

| J | K | Q(t) | Q(t+1) |

| b1 | |||

| b2 | |||

| b3 | |||

| b4 |

| ____ | _ | |||

| Q(t+1) = J* | Q(t) | v | K | *Q(t) |

В интегральной схемотехнике применяются только тактируемые (синхронные) JK триггера, которые при C=0 сохраняют свое состояние, а при C=1 работают как асинхронные JK триггера.

Триггер JK относится к разряду универсальных триггеров, поскольку на его основе путем несложной внешней коммутации можно построить RS-, D— и T— триггера. RS-триггер получается из триггера JK простым наложением ограничения на комбинацию входных сигналов J=K=1, так как эта комбинация является запрещенной для RS триггера.

Счетный триггер на основе JK триггера получается путем объединения входов J и K.

Триггер задержки (D-триггер) строится путем подключения к входу K инвертора, на который подается тот же сигнал, что и на вход J. В этом случае вход J выполняет функцию входа D, а все устройство в целом реализует таблицу переходов D-триггера.

Структурная схема конечного автомата

В структурной теории автомат представляют в виде композиции двух частей: запоминающей части, состоящей из элементов памяти, и комбинационной части, состоящей из логических элементов:

Комбинационная схема строится на логических элементах, образующих функционально полную систему, а память – на элементарных автоматах, обладающих полной системой переходов и выходов.

Каждое состояние абстрактного автомата ai, где i={0, n}, кодируется в структурных автоматах набором состояний элементов памяти Qi, r={1,R}. Поскольку в качестве элементов памяти используются обычные триггера, то каждое состояние можно закодировать двоичным числом ai = Q1a1Q2a2… Qrar. Здесь аi={0, 1}, a Q – состояние автомата . Отсюда:

| __ | ||

| Qa = | Q | ,еслиa=0 |

| Q | ,еслиa=1 |

Общее число необходимых элементов памяти можно определить из следующего неравенства . Здесь (n+1) – число состояний. Логарифмируя неравенство получим . Здесь ]C [ — означает, что необходимо взять ближайшее целое число, большее или равное C.

В отличии от абстрактного автомата, имеющего один входной и один выходной каналы, на которые поступают сигналы во входном X={x1,x2,…,xm} и выходном Y={y1,y2,…,yk} алфавитах, структурный автомат имеет L входных и Nвыходных каналов. Каждый входной xj и выходной yj сигналы абстрактного автомата могут быть закодированы двоичным набором состояний входных и выходных каналов структурного автомата.

| xi = o1a1 o2a2… oLaL |

| yg = Z1a1Z2a2… ZNaN |

Здесь ofи Zh– состояния входных и выходных каналов соответственно.

Очевидно число каналов L и N можно определить по формулам ; , аналогичным формуле для определения R.

Изменение состояния элементов памяти происходит под действием сигналов U=(U1,U2,…,Ur), поступающих на их входы. Эти сигналы формируются комбинационной схемой II и называются сигналами возбуждения элементарных автоматов. На вход комбинационной схемы II, кроме входного сигнала xj, по цепи обратной связи поступают сигналы Q=(Q1, Q2, …, QR), называемые функцией обратной связи от памяти автомата к комбинационной схеме. Комбинационная схема I служит для формирования выходного сигнала yg, причем в случае автомата Мили на вход этой схемы поступает входной сигнал xj, а в случае автомата Мура – сигнал xj не поступает, так как yg не зависит от xj.

Устройство и принцип работы JK-триггера

Наиболее сложный по конструкции триггер широко используется в цифровой технике благодаря своей универсальности. Это, так называемый, JK-триггер.

К уже известным входам R (Reset) – сброс, S (Set) – установка, С – тактовый вход добавлены ещё два. Это входы J (Jump) и K (Kill).

Благодаря наличию этих дополнительных входов появляется возможность несложными схемными средствами достигать интересных результатов.

Логика работы основных входов (C, J, K) реализована следующим образом. Если на входе J высокий потенциал, а на входе K – ноль, то триггер установится в единичное состояние по спаду тактового импульса на входе С. Если на входе J – ноль, а на входе К высокий потенциал то по спаду тактового импульса триггер “сбросится” в нулевое состояние. Когда J=K=0 независимо от тактовых импульсов состояние триггера не меняется. И если J=K=1, то при приходе каждого тактового импульса состояние триггера меняется на противоположное. В этом случае триггер работает как делитель частоты на два.

Благодаря такой логике работы появляется возможность довольно гибко настраивать алгоритм работы триггера. Такая универсальность позволяет использовать JK-триггер в устройствах со сложной логикой работы.

На JK-триггерах несложно реализовать делитель частоты на десять. Если мы подадим на вход импульсы с частотой 10 кГц, то на выходе получим уже 1 кГц. Такие схемы называют декадным делителем или декадой.

Делители с различным коэффициентом пересчёта раньше активно использовались радиолюбителями при изготовлении электронных часов и несложных музыкальных инструментов. Данная схема очень неэкономична и займёт много места, если собирать её на дискретных элементах, так как в ней используется четыре триггера и элемент 2И.

В широко распространённую серию К155 на базе ТТЛ логики входит универсальный JK-триггер К155ТВ1 (КМ155ТВ1). Зарубежными аналогами этой микросхемы являются SN7472N, 7472, SN7472J. Этот триггер построен по двухступенчатой схеме и имеет сложную входную логику, где три входа J и три входа K объединены по схеме логического И. Кроме того триггер имеет прямой и инверсный выходы, входы установки и сброса (S и R) и вход тактовых импульсов С. Вот так он обозначается на схеме.

Вот так выглядит его внутренняя структура. Те, кто знаком с базовыми логическими элементами и устройством простейшего RS-триггера разберутся в устройстве JK-триггера без особых трудностей.

Этот триггер, как видно на схеме, организован на основе логических элементов И – НЕ с различным числом входов. В схеме присутствуют элементы: 2И – НЕ, 3И – НЕ, и 6И – НЕ. Наличие элементов 6И – НЕ, а также двухступенчатой структуры делает триггер многоцелевым и универсальным. В зависимости от конечной задачи, входы триггера могут объединяться или подключаться к другим логическим элементам схемы.

На микросхеме К155ТВ1 можно собрать несложную схему наглядно демонстрирующую работу JK-триггера. Как у почти всех микросхем этой серии 7 вывод – это корпус, а 14 вывод – это напряжение питания +5V. На 12 вывод (вход тактовых импульсов), и на прямой и инверсный выходы триггера, (выводы 8 и 6), необходимо подключить светодиоды через токоограничивающие резисторы.

После подключения питания один из выходных светодиодов загорается. Теперь можно проверить работу триггера по входам установки и сброса. Для этого необходимо поочерёдно подавать на выводы 2 (R) и 13 (S) низкий потенциал или “корпус”.

Светодиодные индикаторы будут попеременно загораться и гаснуть, индицируя в каком состоянии находится триггер. Это проверка работоспособности. Теперь можно посмотреть работу триггера в счётном режиме. Для этого можно объединить входы J и K и соединить их с напряжением питания +5V через резистор.

Этого можно и не делать. По определению любой вывод микросхемы ТТЛ-логики, если он просто “висит” в воздухе и никуда не подключен, находится под высоким потенциалом (уровень логической единицы). Соединение свободных выводов микросхем с плюсом источника питания производится для предотвращения случайных срабатываний, то есть для повышения помехозащищённости.

Теперь можно подать на вход С импульсы такой частоты, чтобы их было визуально видно по работе светодиода HL1. Светодиоды, подключенные к выходам триггера, будут срабатывать с частотой в два раза меньше. То есть в этом режиме JK-триггер делит частоту входного сигнала на два.

Для тестирования триггера понадобится источник внешнего тактового сигнала, чтобы подать последовательность импульсов на вход C.

Простейший генератор прямоугольных импульсов можно собрать, используя микросхему К155ЛА3.

Она содержит четыре элемент 2И – НЕ. Для генератора достаточно двух элементов. Период следования импульсов можно ориентировочно рассчитать по формуле T=1,4*R1*C1. Частота генератора прямоугольных импульсов в таком случае приблизительно будет равна f = 1/T. Для тех номиналов резистора R1 и конденсатора C1, что показаны на схеме, период генератора ориентировочно равен: T = 1,4 * 1000 * 0,00047 = 0,658 (с). Частота f = 1/0,658 = 1,5197… ~ 1,5 (Гц). В дальнейшем этот простейший генератор можно использовать для проверки работоспособности различных цифровых устройств.

Возможности

Также важным отличием данных моделей является то, что в них устранена неопределенность, которая может возникнуть в случае, если входные сигналы будут поданы в определённой комбинации. Также существенным преимуществом является тот факт, что они могут выполнять функционал T-, D- и RS-триггеров. Комбинированный тип имеет дополнительные асинхронные входы, которые используются для предварительной установки приборов в определённое состояние. Примитивный JK можно получить из RS, у которого есть динамическое управление. Для этого необходимо его дополнить обратными связями с выходов на входы. Для получения Т-триггера необходимо на входы подать уровень напряжения, который установит логическую единицу.

В каких состояниях может быть главный герой статьи? Существует два принципа действий: асинхронный и синхронный. Во время первого происходит обмен данных независимо от входов. Синхронный JK-триггер действует одновременно, и из-за требований он является основным используемым элементом.

Чтобы своими глазами увидеть, что и как работает, необходимо JK-триггер включить на макетной плате и собственноручно подавать различные входные сигналы. Это сродни обучению на гитаре – можно изучить десятки самоучителей, но пока не возьмете в руки гитару, вы никогда не научитесь. Так же и со схемами: без опыта разобраться во всём сложно. Для наблюдения можно подсоединить светодиодные индикаторы к инверсному и прямому выходу. При желании положение дел можно наблюдать и благодаря обычному вольтметру, но в связи с размерами данный вариант не очень удобный, если говорить о такой вещи, как JK-триггер.

Таблица истинности

Что такое таблица истинности? Это специальный набор данных, который описывает логическую функцию. Что под ней понимают? В данном случае имеют в виду функцию, в которой значения параметров и её самой выражают логическую истинность. В качестве примера очень к месту будет вспомнить двузначную логику, где можно дать только два определения: ложь или истина. В качестве заменителей, когда говорят о компьютерных технологиях, часто вводят понятие 0 или 1. Причем использование данного инструментария оказалось удобным не только с позиции логики, но и при изображении в табличном варианте. Особенно часто их можно встретить в булевой алгебре или аналогичных системах логики. Но хватит информации, давайте посмотрим, как выглядит таблица JK-триггера.

| J | K | C | Q(t) | Q(t+1) | Пояснения |

| ноль | х | ноль | ноль | ноль | Хранится информация |

| ноль | х | ноль | единица | единица | |

| ноль | ноль | единица | ноль | ноль | Хранится информация |

| ноль | ноль | единица | единица | единица | |

| единица | ноль | единица | ноль | единица | Установлена логическая единица, вход J равен единице |

| единица | ноль | единица | единица | единица | |

| ноль | единица | единица | ноль | ноль | Устанавливается логический нуль, при этом K равно единице |

| ноль | единица | единица | единица | ноль | |

| единица | единица | единица | ноль | единица | счетный режим триггера K=J=1 |

Области применения триггера

JK-триггер можно рассматривать как ячейку памяти объёмом в 1 бит. Подача управляющих сигналов позволяет устанавливать значение памяти, равное 0 или 1, сохранять или инвертировать его, что наглядно демонстрирует таблица переходов.

На практике JK-устройства выпускают в виде микросхем, действующих в соответствии с таблицей истинности синхронного триггера. Обычно для того, чтобы запрограммировать определённый алгоритм сначала составляют логическую формулу преобразования двоичных сигналов. Затем реализовывают её в виде платы, включающей в себя установку триггеров.

Триггеры нашли широкое применение в таких компонентах вычислительных систем, как счетчики, регистры, процессоры и ОЗУ. Универсальность JK-триггеров позволяет использовать их в устройствах с разным уровнем сложности логики работы. Например, на основе JK-триггера можно собрать делитель частоты на 10. При поступлении на вход данного устройства импульсов частотой 10 кГц на выходе будут получены значения, равные 1 кГц. Подобные схемы получили название декадного делителя или декады.

Использование JK-устройств в составе цифровых счетчиков – это их основная область применения. Цифровые схемы в современной технике собираются на основе микросхем программируемой логики (FPGA) или заказных микросхем (ASIC).

Еще одна облать применения JK-триггеров — устройства для обнаружения коротких импульсов. В данном случае импульс после поступления на вход С переходит в единичное состояние, которое затем обнаруживается последующей схемой, например, микропроцессором. Подобно схеме обнаружения КИ работает и схема ждущего мультивибратора.

При создании сложных логических схем нужны приборы разных видов. Поэтому выгоднее использовать универсальный тип устройства, которое может работать в различных режимах. Именно такими устройствами являются JK-триггеры.

Предыдущая