Определение

Что такое триггер? Триггером называют электронное устройство, обладающее способностью довольно долгое время находиться в 1-ом из 2-х стабильных состояний, а так же чередовать их из-за воздействия какого-то внешнего сигнала. Триггер — это по сути простая электроника, от которой зависит работоспособность более сложных систем

Он способен хранить двоичную информацию (ноль или один) после того, как перестанут действовать входные импульсы. Основное назначение устройства, это переключение из одного состояния в другое. Хранит триггер в своей памяти 1 бит информации, которые и определяют его текущее состояние: логический «0» или логическая «1».

Какие входы есть у триггера? Любой триггер может иметь несколько входов, которые бывают:

- Информационными. Они отвечают за общее состояние устройства в момент работы всей цепи.

- Управляющими. Отвечают за установку триггера в предварительное положение и за его дальнейшую синхронизацию.

Работа устройства строится на 2 элементах «И-НЕ», 2 «ИЛИ-НЕ» и других, некоторые разновидности триггеров работают на логических элементах КМОП, ТТЛ, ЭСЛ. Принцип работы любого триггера зависит от количества входов/выходов, а также от типа самого устройства.

В электронике используются устройства на транзисторах или микросхемах. Транзисторные модели применяются при сложных интегральных схемах старого типа. Логическая микросхема обладает меньшими габаритами, хранит информацию без перегрева и перегрузок. Поэтому их используют в более миниатюрных и сложных цепях современной электроники.

Классификация и типы синхронизации триггеров

Триггеры делятся на два больших класса:

- асинхронные;

- синхронные (тактируемые).

Принципиальное различие между ними в том, что у первой категории устройств уровень выходного сигнала меняется одновременно с изменением сигнала на входе (входах). У синхронных триггеров изменение состояния происходит только при наличии сихронизирующего (тактового, стробирующего) сигнала на предусмотренном для этого входе. Для этого предусмотрен специальный вывод, обозначаемый буквой С (clock). По виду стробирования синхронные элементы делятся на два класса:

- динамические;

- статические.

У первого типа уровень выхода меняется в зависимости от конфигурации входных сигналов в момент появления фронта (переднего края) или спада тактового импульса (зависит от конкретного вида триггера). Между появлением синхронизирующих фронтов (спадов) на входы можно подавать любые сигналы, состояние триггера не изменится. У второго варианта признаком тактирования является не изменение уровня, а наличие единицы или нуля на входе Clock. Также существуют сложные триггерные устройства, классифицируемые по:

- числу устойчивых состояний (3 и более, в отличие от 2 у основных элементов);

- числу уровней (также более 3);

- другим характеристикам.

Сложные элементы имеет ограниченное применение в специфических устройствах.

Триггер – простейшее устройство, представляющее собой цифровой автомат. Оно имеет два состояния устойчивости. Одному из этих состояний присваивается значение «1», а другому «0». Состояние устройства, а также значение двоичной информации, которая в нем хранится, определяется выходными сигналами: прямым и инверсным. В том случае, когда на прямом выходе установится потенциал, который соответствует логической единице, в таком случае состояние триггера называется единичным (при этом потенциал на инверсном выходе соответствует логическому нулю). Если же на прямом выходе нет потенциала, то состояние триггера называется нулевым.

Классифицируют триггеры по следующим признакам:

1. По способу записываемой информации (асинхронные и синхронные).

2. По способу управлением информацией (статистические, динамические, одноступенчатые, многоступенчатые).

3. По способу реализации логических связей (JK-триггер, RS-триггеры,Т-триггер, D-триггер и других типов).

Основными параметрами всех типов триггеров являются: максимальная длительность входного сигнала, время задержки необходимого для переключения триггера, а также разрешающее время срабатывания.

В этой статье поговорим о таком типе устройств, как – Т-триггер. Такие триггеры имеют всего один информационный (Т) вход, который называют счетным входом. Он изменяет свое исостояние после поступления на счетный (Т) вход каждого управляющего сигнала.

Согласно таблицы переходов, закон функционирования таких триггеров описывается характеристическим уравнением: Q(t+1)=TtQ’t V T’tQt. Из уравнения следует, что при поступлении на вход (Т) логического нуля, Т-триггер сохранит свое состояние, а при подаче логической единицы, изменит на противоположное.

| Qt | Tt | Q(t+1) |

| 1 | 1 | |

| 1 | 1 | |

| 1 | 1 |

Из таблицы видно, что Т-триггер выполняет операцию сложения, это и обусловило название такого триггера счетным, его информационный (Т) вход– счетным входом. Уровень сигнала на входе такого триггера появляется в два раза чаще, чем на его выходе (Q). Соответственно Т-триггер используют в качестве делителя частоты.

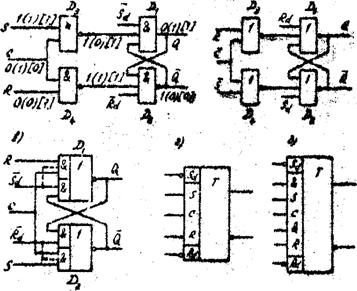

Т-триггер асинхронного типа может быть сконструирован на базе двухступенчатого триггера RS с дополнительными связями, а именно: выход триггера (Q) необходимо соединить со входом (R), а выход (Q’) со входом (S). Информационным входом (Т) будет являться синхронный вход (С).

На фото изображен Т-триггер. Схема функциональная.

В исходном состоянии на информационных входах триггера (R и S) подается уровень логического нуля, при подаче на счетный (Т) вход логического нуля, будет происходить постоянное копирование состояния первого триггера вторым триггером, потому что элемент И-НЕ будет выдавать уровень логической единицы на вход второго триггера. Если Т-триггер находился в состоянии единицы, то на входы (R и S) будет подаваться уровни нуля и единицы соответственно. При поступлении на счетный вход первого сигнала равного логической единице, в первый триггер запишется логическая единица. Состояние же второго триггера не изменяется, потому что уровень нуля с выхода логического элемента И-НЕ блокирует его состояние. После снятия счетного импульса на входе (Т) устанавливается нуль, и второй триггер переключается в состояние логической единицы.

Синхронные Т-триггеры используют в случае необходимости представлять потенциалом

Разновидности

Для того чтобы разобраться как работает триггер, необходимо понять к какому классу и типу он относится. Существуют 2 основных класса этих устройств:

- Синхронные с двумя основными классами: статическими и динамическими.

- Асинхронные.

Обе разновидности имеют схожий принцип работы. Отличие заключается только в процессе перехода сигнала из одного состояния в другое. Асинхронные делают это напрямую, а синхронные работают исходя из этого сигнала.

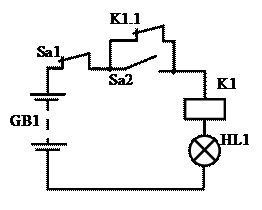

Триггер — электронная схема, имеющая несколько устойчивых состояний, сохраняющихся длительное время (пока включено электропитание схемы). Соответственно триггеры могут выполнять функцию элементов памяти. В цифровой технике используются бистабильные триггеры с двумя устойчивыми состояниями, которые кодируют значения логических «0» и «1». Триггеры могут быть построены на дискретных элементах (транзисторные каскады) и на логических элементах — цифровые триггеры. Также триггер может быть представлен в виде электромеханической аналогии (релейной схемы).

Рисунок 1. Электромеханическая аналогия RS – триггера

1 Классификация триггеров.

Триггеры различаются по логике работы и по способу приема и запоминания информации. Ниже представлена классификация триггеров, предложенная в книге Е.Угрюмова «Цифровая схемотехника». В ней выделены наиболее популярные типы триггеров, однако количество их разновидностей гораздо больше.

а) По логике работы:

1) RS — с раздельными входами записи «1» — «установки» (вход S) и записи «0» -«сброса» (сигнал R).

2) D — триггер задержки информационного сигнала (Delay).

3) T — тактируемый (Tact) или счетный триггер.

4) JK — универсальный триггер.

5) комбинированный — например, RST — тактируемый со входами «установки» и «сброса».

6) со сложной логикой — с группами входов, связанных логическими зависимостями. Например, JK-триггер с тремя входами J и тремя K, связанными конъюнкцией: (J1*J2*J3) и (K1*K2*K3).

б) По способу приема информации:

1) Асинхронные (нетактируемые) — переход в новое состояние происходит по изменению состояния управляющих (информационных) входов.

2) Синхронные (тактируемые) — переход в новое состояние под воздействием информационных входов происходит по только сигналу на специальном тактовом (синхронизации) входе (С / CLK / CLOCK).

Примечание: у реальных триггеров наряду с синхронизируемыми информационными входами сохраняют асинхронные информационные входы, чтобы обеспечить асинхронную установку или сброс триггера при реинициализации системы («сброс» или включение питания).

— Синхронные управляемые уровнем — при одном уровне тактового сигнала триггер воспринимает состояние управляющих входов, а при другом — не воспринимает и остается в одном состоянии, сохраняя записанную в него информацию. Типичный триггер управляемый уровнем — «триггер-защелка» (latch).

— Синхронные управляемые фронтом — При управлении фронтом переходы из состояния в состояние происходят по фронту тактового сигнала.

в) По внутренней структуре:

1) Одноступенчатые: в их внутренней структуре одна запоминающая схема, которая переключает свое состояние (запоминает данные) под влиянием управляющих сигналов. По одноступенчатой схеме строятся асинхронные триггеры и синхронные управляемые уровнем.

2) Двухступенчатые (или многоступенчатые) триггеры состоят из двух одноступенчатых триггеров. При переключении двухступенчатого триггера сначала переключается первая, а только следом — вторая. Это позволяет записывать данные только по фронту синхроимпульса, не реагируя на изменения на информационных входах в течении синхроимпульса. Т.е. по многоступенчатой схеме строятся синхронные управляемые фронтом триггеры. Это наиболее применяемый сегодня тип триггеров.

2 Структура триггера.

Триггеры состоят из двух блоков: схемы памяти (фиксатора) и схемы управления.

Электрически элемент памяти любого триггера это схема с положительной обратной связью. В частности, фиксатор цифрового триггера представляет собой два соединенных «крест-накрест» элемента НЕ (см. Рисунок 2, а).

Если на выходе одного элемента НЕ установилась «1», то она попадет на вход второго элемента НЕ и на его выходе будет «0», который, в свою очередь попадет на вход первого элемента НЕ и удержит на его выходе «1». Таким образом схема находится в устойчивом состоянии, которое будет сохраняться бесконечно долго — пока на схему памяти подано электропитание. Если же на выходе первого элемента изначально установился «0», то на выходе второго элемента будет «1», т.е. схема памяти переключится в противоположное состояние.

Если принять выход одного из этих элементов (допустим первого по описанию, приведенному выше) как выход всей схемы, то в первом из описанных устойчивых состояний схема памяти запомнит «1», а во втором запомнит «0». Выход второго элемента НЕ всегда будет в противоположном состоянии относительно выхода — его называют инверсным выходом. Выход (или «прямой» выход) обозначают Q. «Инверсный» выход обозначают nQ.

Схема из двух инвертеров не позволяет переключать ее из одного состояния в другое. Чтобы выполнить это, элементы НЕ заменяют элементами И-НЕ или ИЛИ-НЕ. Соответственно у схемы памяти появляются два входа, один из которых (этот вход называют входом «установки» — SET или S) выполняет переключение схемы в состояние «1» на выходе, а другой (этот вход называют входом «сброса» — RESET или R) — в состояние «0» не выходе.

Рассмотрим работу схемы с элементами ИЛИ-НЕ. Входы SET и RESET будут иметь активный уровень «1» и неактивный «0». Когда на входы R и S подан неактивный уровень логического «0» значение на выходе будет непредсказуемым — оно установится случайным образом при включении электропитания. Если для вышерассмотренной схемы на вход первого элемента ИЛИ-НЕ подать «1», то на выходе Q установится «0», а на nQ -«1», т.е. триггер запомнит «0» и будет сохранять это значение, даже если вход перейдет в неактивное состояние «0». В соответствии с таким действием данный управляющий вход называют R (Reset или Сброс). Если же «1» подать на второй вход, то на выходе Q установится и будет «запомнена» логическая «1» (nQ = 0), которая сохранится при переходе входа S в неактивное состояние «0». Соответственно этот вход называют S (Set или Установка).

Есть две важных особенности использования элемента памяти:

1. Если на входы R и S нельзя одновременно подать активные сигналы, фиксатор перейдет в состояние, когда на обоих выходах будет «1». Такое состояние считается недопустимым, так как на выходах Q и nQ должно быть противоположное значение. Кроме того, при снятии активных уровней с обоих входов R и S одновременно, невозможно предсказать, в какое состояние переключится элемент памяти.

2. Переключения фиксатора — «запоминание» — происходит в момент перехода управляющего сигнала R или S в активный уровень, и после этого, элемент памяти не изменяет своего состояния вне зависимости от того сохранился ли активный уровень на входе R или S или опять стал пассивным.

Аналогично описанной схеме работает и схема памяти на базе элементов И-НЕ. Разница только в полярности управляющих сигналов: в данном случае активным уровнем управляющих сигналов будет «0» и они будут соответственно называться nR и nS.

Описанная выше схема памяти является простейшим триггером — его называют триггером RS-типа или RS-триггером. RS-триггер достаточно неудобен в управлении, но может быть усовершенствован и преобразован в другие типы триггеров путем подключения дополнительной схемы управления. Таким образом RS-триггер основа большинства триггеров других типов.

Данная схема памяти имеет два независимых управляющих входа R и S, записывающих в нее «0» и «1» соответственно.

Однако использование только входов R и S не всегда удобно и сильно ограничивает возможности по запоминанию значений и по использованию триггеров в последовательностных схемах. Поэтому добавляют схему управления, которая преобразует более сложные комбинации управляющих сигналов, в том числе последовательности сигналов, в описанные сигналы R и S. Схема управления задает как логику (правила реакции на входные сигналы) работы триггера, так и способ приема информации триггером.

3. Асинхронные и синхронные управляемые фронтом триггеры

3.1. RS-триггеры.

Функционирование и внутренняя схема асинхронного RS — триггера соответствует описанной выше схеме памяти. Данный тип триггера фактически не имеет схемы управления на входе.

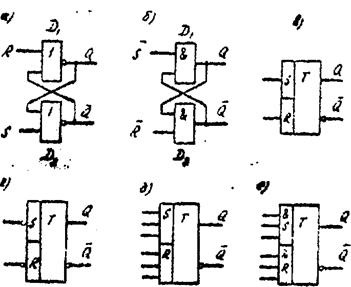

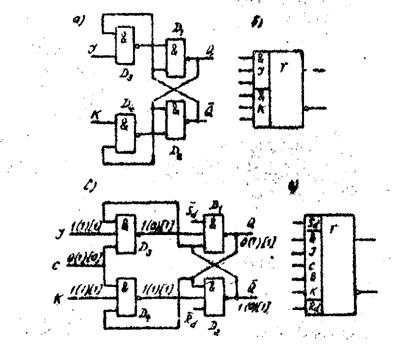

Рисунок 2 Асинхронные RS-триггеры на элементах И-НЕ (а), ИЛИ-НЕ (б) и их условные обозначения (в, г)

Синхронные RS — триггеры с управлением уровнем имеют вход синхронизации (С), сигнал на котором разрешает управление с информационных входов, пока находится в активном состоянии. Входные информационные сигналы «пропускаются» через логические вентили И (для схемы на базе элементов ИЛИ-НЕ, активный уровень (С) = 1) или через вентили ИЛИ (для схемы на базе элементов И-НЕ, активный уровень (С) = 0).

Характерной особенностью триггерных схем, управляемых уровней синхроимпульса, является то, то изменение уровней информационных сигналов в течение действия синхроимпульса приводит к изменению состояния триггера. Если по фронту синхросигнала в триггер было занесено значение «1», и далее в течение удержания активного уровня синхросигнала C информационные сигналы приняли значения R =1, S =0, то это приводит к переключению триггера в состояние «0». Следовательно, для обеспечения работы триггера сигналы R и S должны оставаться неизменными в течении активного уровня синхроимпульса, а изменяться в течение паузы между синхроимпульсами.

Рисунок 3 Синхронные RS-триггеры с управлением уровнем на элементах И-НЕ (а), ИЛИ-НЕ (б) и их условные обозначения (в, г)

Синхронный RS-триггер с управлением по фронту построен по многоступенчатой схеме, описанной ниже.

RS-триггеры редко используются как самостоятельные элементы, но, как говорилось выше, являются элементом памяти (фиксатором) в составе других типов триггеров.

3.2. D-триггеры.

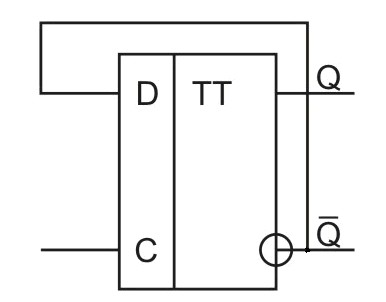

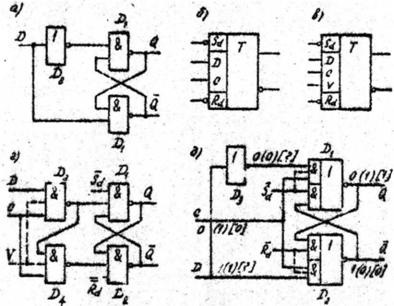

D-триггером (или триггером задержки сигнала) называют триггер с одним информационным входом (D) и входом синхронизации (С). По импульсу синхронизации © состояние на входе (D) сохраняется в триггере и устанавливается на выходе (Q). Состояние выхода Q останется неизменным до следующего импульса на входе синхронизации. Как видно из описания D-триггер является синхронным (обязательно используется сигнал синхронизации). Можно построить также схему асинхронного D-триггера (см. Рисунок 4 а)), но она будет иметь смысл только как повторитель с задержкой на переключение, а не как схема памяти. Асинхронные D-триггеры почти не используются.

Из широко применяемых первый — D-триггер с управлением по уровню, так же называемый «триггер-защелка» (LATCH) (см. Рисунок 4 г). Он прозрачен для входного информационного сигнала пока сигнал синхронизации © в активном состоянии и защелкивает значение на выходе (Q) в момент перехода (С) в неактивное состояние. Такой D-триггер представляет собой RS-триггер с синхронизацией по уровню, у которого на вход S подключен информационный сигнал (D), а на вход ® — инвертированный информационный сигнал. То есть в схему управления добавляется один инвертор «по входу». Входы Rd и Sd используются для асинхронных сброса или установки триггера в определенное состояние и удержание его в этом состоянии, если требуется. Для устойчивой работы такого D-триггера необходимо, чтобы состояние входа D не изменялось в момент действия синхроимпульса на входе С.

Рисунок 4 Асинхронный (а) и управляемые уровнем синхроимпульса (г, д) D-триггеры и их условные обозначения (б, в)

Для расширения функциональности к D-триггеру можно добавить вход разрешения V. При активном уровне (в данном случае «1») на данном входе триггер работает в вышеописанном режиме, при V = «0», триггер не реагирует на входы С и D. Поведение DV-триггера описывается формулой Qn+1 = DnVn Qn .

Второй тип, наиболее часто используемый — D-триггер с управлением по фронту синхросигнала, так называемый FLIP-FLOP. Данные записываются в него в момент перепада синхросигнала и сохраняются неизменными до следующего фронта. Такие триггеры строятся по двухступенчатой схеме и будут описаны ниже.

D-триггер является одним из самых широко используемых типов. Такие триггеры выпускаются отдельные микросхемы, а также являются базовыми структурными элементами многих ПЛИС. Несколько D-триггеров, с объединенными тактирующими входами образуют многоразрядные регистры: синхронные регистры (управление по уровню) или регистры-защелки (управление по фронту).

3.3. Т-триггеры.

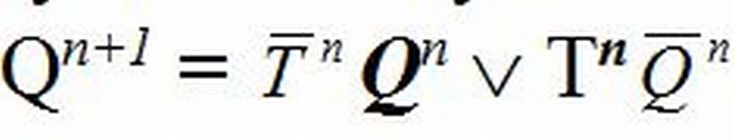

Т -триггер представляет собой схему с одним логическим входом Т. Так как этот триггер работает в режиме учета импульсов на входе, его иногда называют счетным триггером (триггером со счетным входом). Т -триггер изменяет свое состояние на противоположное после воздействия импульса, поступающего на вход Т, т.е. его функционирование описывается формулой:

Схема простейшего Т -триггера с элементами задержки и в цепях обратной связи приведена ниже (см. Рисунок 5). Элементы задержки обеспечивают надежноепереключение триггера, причем время задержки tз на этих элементах должно быть больше длительности синхроимпульса на входе Т

Рисунок 5 Т- и ТV-триггеры, управляемые уровнем синхроимпульса

Пусть Q = 1, Q`= 0. Поступающий на счетный вход импульс приводит к появлению нулевого сигнала на выходе элемента D4 (на его входах — две «1») и последовательной установке сигналов Q = 1, Q`= 0, т.е. к опрокидыванию триггера в нулевое состояние. При этом сигнал на входе D3 не изменяется, так как на его входе в течение tз действует нулевой сигнал, поступающий с выхода Q` через элемент задержки D5.

После окончания действия счетного импульса сигналы на выходах элементов D3 и D4 принимают единичные значения, а на вход D3 через элемент задержки D5 поступает разрешающий уровень с выхода Q`. В результате следующий счетный импульс перебросит триггер в исходное состояние.

Элементы D5 и D6 обеспечивают задержку появления сигналов обратной связи с тем, чтобы в течение действия счетного импульса не происходило многократного переключения триггера. В интегральных триггерах роль элементов задержки могут выполнять либо логические элементы, либо специальные полупроводниковые приборы с накоплением заряда. Однако, в силу жестких ограничений на длительность импульса на счетном входе и сложности реализации элементов задержки, Т-триггеры на базе RS-триггера с управлением уровнем синхросигнала почти не используются, а применяются триггеры с управлением по фронту синхросигнала.

ТV-триггер является разновидностью Т-триггера с дополнительным входом разрешения счета. Принцип его работы аналогичен DV-триггеру, описанному выше.

4.3.4. JK-триггеры.

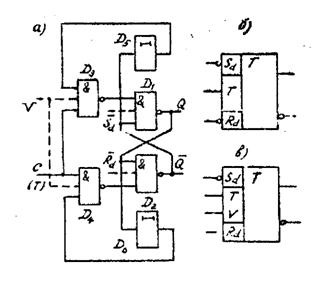

JK -триггер похож на RS — триггер (вход J эквивалентен входу S, а вход К — входу R), но не имеет запрещенного состояния К®=1, J(S)=1. При условии J=K=1 триггер осуществляет инверсию предыдущего состояния, а при остальных комбинациях входных сигналов функционирует в соответствии с таблицей истинности RS -триггера.

JK -триггер можно получить из RS -триггера, связав выходы триггера с его входами обратной связью. При этом схема управления должна быть построена таким образом, чтобы на входах R и S единичные сигналы одновременно не появлялись. Тогда при J = K =1 схема управления принуждает триггер работать в режиме переключения (счетный режим), так как, благодаря связи с выхода на вход, учитывается предшествующее состояние схемы, и сигнал направляется на соответствующий вход RS -триггера, вызывая его переключение.

Принципиально можно построить асинхронный JK -триггер (см. Рисунок 6 а), но они очень неустойчивы практического применения не находят: для нормальной работы асинхронного триггера в счетном режиме длительность управляющих сигналов не должна превышать времени переключения триггера, что очень сложно обеспечить на практике. В противном случае схема будет непрерывно переходить из одного состояния в другое, пока хотя бы один из сигналов не станет равным нулю.

Рисунок 6 Асинхронный (а) и синхронный с управлением уровнем импульса (в) JK-триггеры и их условные обозначения (б, г)

Синхронный вариант JK -триггера с управлением уровней синхроимпульса получается из асинхронного путем добавления входа для подачи синхроимпульсов (Рисунок 6.в). В этой схеме занесение информации в триггер происходит при поступлении синхроимпульса. Максимальная длительность синхроимпульса должна быть чуть меньше, чем задержка в цепочке D1(D2)+D4(D3). Превышение этой величины вызывает появление ложного сигнала на выходе элемента D4(D3), что может привести к повторному переключению триггера. С другой стороны, длительность синхроимпульса ограничена по минимуму задержкой цепочки D1+D2, чтобы успел переключиться триггер. Чтобы выполнить эти условия на практике потребуется подбирать задержки элементов (причем, у D3 и D4 они должны быть больше чем у D1 и D2) и длительность синхроимпульса. Учитывая большие разбросы временных параметров, выполнить все условия на практике не представляется возможным. Поэтому рассмотренные синхронные JK -триггера также как и асинхронные на практике фактически нереализуемы. Работоспособность JK -триггеров обеспечивается только в схемах, управляемых фронтом (срезом) синхроимпульса.

Асинхронные

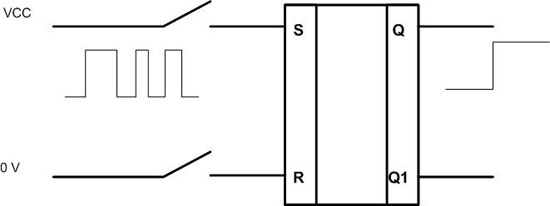

Асинхронные RS-триггер имеет 2 основных входа «R» и «S». Также предусматриваются выходы «Q» и «Q−». Устройство RS триггера позволяет выполнять следующую последовательность:

- Вход «S» является установочным. На него подается высокое напряжение, вследствие чего логический выход «Q» устанавливается как «1».

- Вход «R» отвечает за сброс положения. Высокое напряжение в виде логической «1» на этом входе предполагает установку 0 на выходе «Q», а на выходе «Q–» – «1».

Асинхронный RS-триггер условно работает следующим образом:

- При подаче напряжения на вход «S» устройство включается и хранит такое состояние даже при потере положительного сигнала.

- При подаче сигнала на вход «R» устройство отключается, при этом сохраняя логический 0 на выходах.

Схема RS-триггера асинхронного типа самая простая. Она работает без синхронизации с дополнительным входом. Используется RS компонент в простых элементах или как дополнение для более сложных триггеров.

Далее будет представлена УГО, таблица истинности и общая схема такого триггера.

Синхронные триггеры

Триггерные схемы с несколькими устойчивыми состояниями

Триггер с числом устойчивых состояний N строится из N элементов (N-1)ИЛИ-НЕ или (N-1)И-НЕ путём соединения выхода каждого элемента (Q0, Q1, …, Q(N-1)) с соответствующими входами всех других элементов.

Триггеры на элементах (N-1)ИЛИ-НЕ работают в прямом одноединичном коде (на выходе Q одного из элементов – “1”, на выходах Q других элементов – “0”).

Триггеры на элементах (N-1)И-НЕ работают в инверсном однонулевом коде (на выходе Q одного из элементов – “0”, на выходах Q других элементов – “1”).

При добавлении N транзисторов доступа эти триггеры могут работать как ячейки статической сверхоперативной памяти.

Практическое использование

Свойство триггеров сохранять записанную информацию даже при снятии внешних сигналов позволяет применять их в качестве ячеек памяти ёмкостью в 1 бит. Из единичных элементов можно построить матрицу для запоминания двоичных состояний – по такому принципу строятся статические оперативные запоминающие устройства (SRAM). Особенностью такой памяти является простая схемотехника, не требующая дополнительных контроллеров. Поэтому такие SRAM применяются в контроллерах и ПЛМ. Но невысокая плотность записи препятствует использованию таких матриц в ПК и других мощных вычислительных системах.

Выше упоминалось использование триггеров в качестве делителей частоты. Бистабильные элементы можно соединять в цепочки и получать различные коэффициенты деления. Та же цепочка может быть использована в качестве счетчика импульсов. Для этого надо считывать с промежуточных элементов состояние выходов в каждый момент времени – получится двоичный код, соответствующий количеству пришедших на вход первого элемента импульсов.

В зависимости от типа примененных триггеров, счетчики могут быть синхронными и асинхронными. По такому же принципу строятся преобразователи последовательного кода в параллельный, но здесь используются только стробируемые элементы. Также на триггерах строятся цифровые линии задержки и другие элементы двоичной техники.

RS-триггеры используются в качестве фиксаторов уровня (подавителей дребезга контактов). Если в качестве источников логического уровня применяются механические коммутаторы (кнопки, переключатели), то при нажатии эффект дребезга сформирует множество сигналов место одного. RS-триггер с этим успешно борется.

Область применения бистабильных устройств широка. Круг решаемых с их помощью задач во многом зависит от фантазии конструктора, особенно в сфере нетиповых решений.

Заключение

С триггерами в жизни мы сталкиваемся довольно часто, ведь они широко используются в различных сферах. В данной статье было приведено описание и области использования различных разновидностей данного устройства. При ремонте электронного оборудования важно знать: для чего нужен этот элемент, где он используется и по какому принципу работают такие устройства.

Предыдущая